- 2011-06-14 11:24

- 作者:佚名

- 来源:互联网

六自由度电磁敏感定位系统作为一种新型的跟踪定位装置,可实时地确定目标的六个参数,已在机载火控系统(头盔瞄准具)、精密医疗器械、单兵作战模拟训练中获得广泛应用[1、2]。该跟踪系统由正弦信号发射电路、敏感信号接收电路组成的硬件和从敏感接收数据中求解目标参数的算法程序两部分组成,定位计算精度受制于上述两部分的误差。目前,在不考虑环境因素影响的情况下,算法误差已达到小于1毫弧的水平,因此,硬件电路的误差成为制约系统定位精度的主要因素。根据工作原理,该系统采取按时序依次激励发射天线,从而根据敏感天线接收信号组成接收矩阵计算目标参数。然而,作为时序控制电路的模拟器件,存在无法避免的温度漂移和时间漂移问题,从而大大影响了时序发射的精度,使系统定位计算的精度降低。为了解决该问题,本文利用CPLD数字控制技术对时序电路进行改进。CPLD(Complex Programmable Logic Device)是新一代的数字逻辑器件,具有速度快、集成度高、可靠性强、用户可重复编程或动态重构其逻辑功能等特点。利用CPLD芯片和数字控制技术设计的时序电路,可将时序控制的精度提高到纳秒级,并且工作稳定,不受温度的影响,有利于系统定位精度的提高。

系统原理

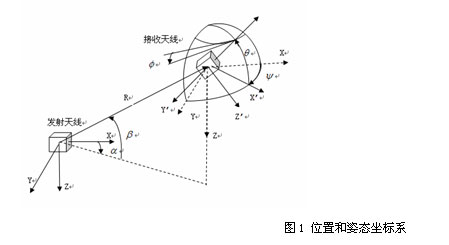

六自由度电磁敏感系统的工作原理[2]如下:以发射天线的三个轴(x、y、z)为参考坐标系,接收天线相对于发射天线的位置参数由距离 、方位角 和仰角 表示,姿态参数由偏航角 、俯仰角 和横滚角 表示,此六个参数即为需要计算的目标参数,即六自由度,参看图1。系统由正弦信号发生器、时序控制电路、功率放大电路、三轴环天线、接收信号放大电路、检波判相电路和数据采集与参数计算电路组成,参看图2。

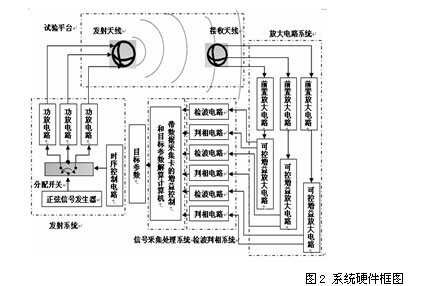

系统工作时,发射电路以时分制激励方式依次激励发射天线的三路环形天线,每激励一次,接收天线(共三路)均收到三个信号,在一个激励周期内接收天线共收到九个信号,由此九个信号组成的接收矩阵可计算出所有的目标参数。

时序控制电路设计

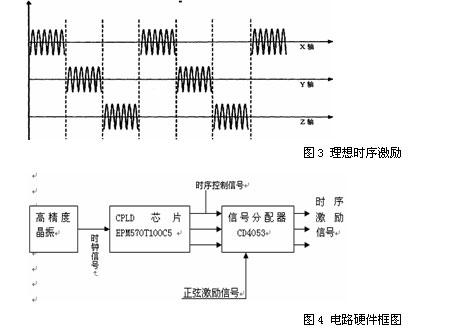

由系统工作原理可知,发射信号需以时分制方式依次激励三路发射天线,因此,时序控制的精确在提高系统跟踪定位计算精度方面显得十分重要。但由于原时序电路采用的电容等模拟元器件的有限精度以及模拟器件受温度影响的结果,时序控制信号会发生漂移,精度较低,从而使接收矩阵元素的实际值与理论值发生较大大偏差,影响了系统的计算精度。要想提高系统定位计算的精度,必须提高系统时序控制的精度,基于此,本文根据CPLD数字控制技术,在MAX II系列芯片EPM570T100C5上设计了一种新型的数字时序控制电路,大大提高了系统时序控制的精度,从而提高了系统计算精度。电路组成如图4所示。

由32MHz高精度晶体振荡器提供精确的时钟信号。MAX II芯片EPM570T100C5产生精确的时序控制信号。EPM570是世界一流的低成本器件,适用于实现任何数字控制功能。该芯片采用非易失单芯片解决方案,可解决处理器I/O引脚不够用等板级问题,管理上电排序,配置其它更复杂的器件,或者低成本实现不兼容接口(“胶合逻辑”)的转换。具有低成本、零功耗、小封装、瞬间启动以及非易失性、系统内可编程能力(ISP)等优点。CD4053根据CPLD芯片提供的精确时序数字控制信号完成正弦信号的时分制激励。

软件设计

在CPLD开发的过程中,使用的是Altera公司提供的CPLD开发软件QuartusⅡ,该软件支持Altera公司的绝大部分器件。为了缩短设计周期和降低设计复杂度,QuartuslI包含了工作组计算、集成逻辑分析功能、EDA工具集成、多工程支持、增强重编译和IP集成等功能。在设计过程中采用的是自顶到底的设计思想,顶层基于功能块的设计,底层的具体功能通过VHDL语言编程实现。

顶层设计

自顶向底的设计过程是在软件中先从系统级功能设计开始,然后分别设计并验证系统中不同的功能块。这种设计方法的好处是可以不断地向设计中添加新的功能模块,完善系统的功能。

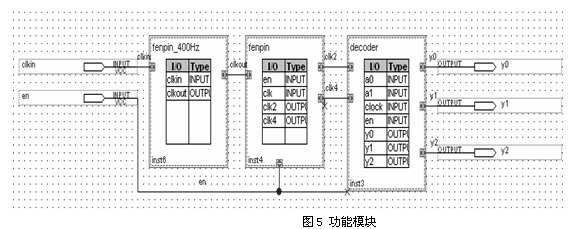

在顶层中主要设计了三个功能模块: 预分频模块、次分频模块、译码模块。功能块图见图5。系统上电工作时,首先由晶振为系统提供精确的基频信号,通过预分频模块将原有基频信号转化为400Hz的时序信号,将400Hz的信号通过次分频模块进行二分频和四分频[6,7],将分频所得100Hz和200Hz的信号输入译码器模块[7],通过译码产生时序间隔为2.5ms的精确时序控制信号。

底层设计

系统功能验证完成后,将抽象的顶层设计向低层设计细化,底层软件设计是基于顶层软件中三大功能模块而设计的,模块设计采用VHDL语言描述完成,通过编译、综合、仿真后生成底层设计文件,以供顶层设计调用。以fenpin模块为例,部分程序如下:

architecture rt of fenpin is

signal temp :std_logic_vector(1 downto 0);

begin

process(clk,temp,en)

begin

if en=’1’ then

if rising_edge(clk) then

temp<=temp+’1’;

end if;

null;

end if;

end process;

clk2<=temp(0);

clk4<=temp(1);

end rt;

系统仿真和验证

软件设计完成后,通过Quartus II软件指定芯片为EPM570T100C5,并根据电路原理图进行引脚分配,设定CPLD的引脚功能,然后启动编译程序来编译项目。编译器将进行错误检查、网表提取、逻辑综合和器件适配,然后进行行为仿真、功能仿真和时序仿真,最后用下载电缆通过JTAG编程方式将文件下载到芯片中,从而生成硬件电路。

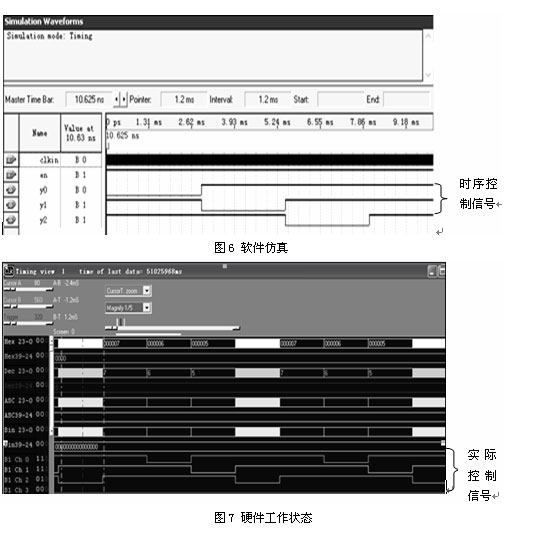

图6为系统软件仿真的结果,从图中可以发现,生成的时序控制信号状态稳定,精度为纳秒级。

图7为将程序下载到目标芯片,硬件工作时通过逻辑分析仪观察到的系统实际工作状态图,可以发现系统实际工作状态与理论设计思想相一致。图中的三路时序控制信号精度较高、状态稳定,无毛刺和漂移现象,为提高系统的稳定性和接收矩阵的精度奠定了基础。